# THIS DOCUMENT IS FOR MAINTENANCE PURPOSES ONLY AND IS NOT RECOMMENDED FOR NEW DESIGNS

# **SP8680A**

# 550MHz÷10/11

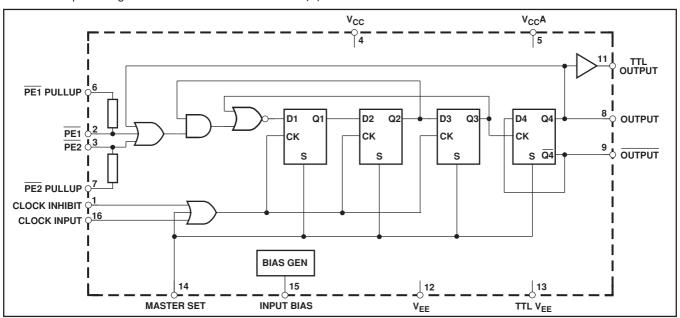

The SP8680A is an ECL variable modulus divider, with ECL and TTL compatible outputs. The circuit can operate from either ECL or TTL supplies. It divides by 10 when either of the ECL control inputs, <u>PE1</u> or <u>PE2</u>, is in the high state and by 11 when both are low (or open circuit). The divider can be set asynchronously to the eleventh state by applying a high level to the master set (MS) input.

#### **FEATURES**

- Very High Speed 650MHz (Typ.)

- ECL and TTL Compatible Inputs/Outputs

- DC or AC Clocking

- Clock Inhibit

- Asynchronous Master Set

- Equivalent to Fairchild 11C90

#### CLOCK INHIBIT 16 CLOCK INPUT INPUT BIAS PE1 **CONTROL INPUTS** PE2 MASTER SET INPUT Vcc 13 V<sub>EE</sub> (TTL O/P) SP8680A O/P STAGE V<sub>CC</sub>A 12 VEE PE1 PULLUP 11 TTL OUTPUT PE2 PULLUP 10 NC **ECL OUTPUT** 9 ECL OUTPUT **DG16**

Fig. 1 Pin connections - top view

# **QUICK REFERENCE DATA**

■ Supply Voltage: -4.75V to -5.5V (ECL), 4.75V to 5.5V (TTL)

■ Power Consumption: 420mW

■ Temperature Range: -55°C to +125°C

## **ABSOLUTE MAXIMUM RATINGS**

####

### **ORDERING INFORMATION**

**SP8680 A DG**

Fig. 2 Functional diagram

# **SP8680A**

# **ELECTRICAL CHARACTERISTICS**

Unless otherwise stated, the Electrical Characteristics are guaranteed over specified supply, frequency and temperature range **ECL OPERATION**

Supply voltage,  $V_{EE} = -4.75V$  to -5.5V,  $V_{CC} = 0V$  Temperature,  $T_{AMB} = -55^{\circ}C$  to  $+125^{\circ}C$

| Characteristic                      | Cumbal           | Value  |        | Units  | Conditions                                                        | Notes |

|-------------------------------------|------------------|--------|--------|--------|-------------------------------------------------------------------|-------|

| Characteristic                      | Symbol           | Min.   | Max.   | Ullits | Conditions                                                        | Notes |

| Maximum frequency (sinewave input)  | f <sub>MAX</sub> | 550    |        | MHz    | AC coupled clock = 350mV p-p                                      | 5     |

| Minimum frequency (sinewave input)  | f <sub>MIN</sub> |        | 10     | MHz    | AC coupled clock = 600mV p-p                                      | 6     |

| Power supply current                | I <sub>EE</sub>  |        | 105    | mA     | $V_{EE} = -5.5V$ , pins 6, 7, 13 o/c                              | 5     |

| ECL output high voltage             | V <sub>OH</sub>  | -0.93  | -0.78  | V      | $V_{EE} = -5.2V (25^{\circ}C), R_{L} = 100\Omega \text{ to } -2V$ |       |

| ECL output low voltage              | $V_{OL}$         | −1.85  | -1.62  | V      | $V_{EE} = -5.2V (25^{\circ}C), R_{L} = 100\Omega \text{ to } -2V$ |       |

| Input high voltage                  | $V_{INH}$        | -0.095 | -0.81  | V      | $V_{EE} = -5.2V (25^{\circ}C)$                                    |       |

| Input low voltage                   | $V_{INL}$        | −1.85  | -1.475 | V      | $V_{EE} = -5.2V (25^{\circ}C)$                                    |       |

| Input low currents                  | I <sub>IL</sub>  | 0.5    |        | μΑ     | 25°C                                                              |       |

| Input high current, clock and MS    | I <sub>H</sub>   |        | 400    | μΑ     | $V_{IN} = -1.85V (25^{\circ}C)$                                   |       |

| Input high current, PE1 and PE2     | I <sub>H</sub>   |        | 250    | μΑ     | $V_{IN} = -0.8V (25^{\circ}C)$                                    |       |

| Propagation delay, clock to Q4 low  | t <sub>pHL</sub> |        | 4      | ns     | $R_L = 100\Omega \text{ to } -2V \text{ (25°C)}$                  | 6     |

| Propagation delay, clock to Q4 high | t <sub>pLH</sub> |        | 3      | ns     | $R_L = 100\Omega \text{ to } -2V \text{ (25°C)}$                  | 6     |

| Propagation delay, MS to Q4 high    | t <sub>pLH</sub> |        | 6      | ns     | 25°C                                                              | 6     |

| Modulus control set-up time         | ts               | 4      |        | ns     | 25°C                                                              | 3, 6  |

| Modulus control release time        | t <sub>r</sub>   | 4      |        | ns     | 25°C                                                              | 4, 6  |

| ECL output rise time (20% - 80%)    | t <sub>ELH</sub> |        | 2      | ns     | 25°C                                                              | 6     |

| ECL output fall time (80% - 20%)    | t <sub>EHL</sub> |        | 2      | ns     | 25°C                                                              | 6     |

## **TTL OPERATION**

Supply voltage,  $V_{CC} = V_{CC}A = 4.75V$  to 5.5V,  $V_{EE} = 0V$  Temperature,  $T_{AMB} = -55^{\circ}C$  to  $+125^{\circ}C$

| Characteristic                       | Cumbal           | Value |      | Units | Conditions                                             |       |

|--------------------------------------|------------------|-------|------|-------|--------------------------------------------------------|-------|

| Characteristic                       | Symbol           | Min.  | Max. | Units | Conditions                                             | Notes |

| Maximum frequency (sinewave input)   | f <sub>MAX</sub> | 550   |      | MHz   | AC coupled clock = 350mV p-p                           | 5     |

| Minimum frequency (sinewave input)   | f <sub>MIN</sub> |       | 10   | MHz   | AC coupled clock = 600mV p-p                           | 6     |

| Power supply current                 | I <sub>CC</sub>  |       | 111  | mA    | $V_{CC} = 5.5V$ , pins 6, 7 o/c, pin 13 to pin 12      | 5     |

| TTL output high voltage              | V <sub>OH</sub>  | 2.3   |      | V     | $V_{CC} = 4.75V$ , $I_{OH} = -640\mu A$                | 5     |

| TTL output low voltage               | V <sub>OL</sub>  |       | 0.5  | V     | $V_{CC} = 5.5V, I_{OL} = -20\mu A$                     | 5     |

| Input high voltage, PE1 and PE2      | V <sub>INH</sub> | 3.9   |      | V     | $V_{CC} = 5.0V (25^{\circ}C)$                          |       |

| Input low voltage, PE1 and PE2       | V <sub>INL</sub> |       | 3⋅5  | V     | $V_{CC} = 5.0V (25^{\circ}C)$                          |       |

| Input low current, PE1 and PE2       | I <sub>IL</sub>  | -4    |      | mA    | $V_{CC} = 5.5V (25^{\circ}C)$ , pins 6, 7 = $V_{CC}$ , |       |

|                                      |                  |       |      |       | $V_{IN} = 0.4V$                                        |       |

| Propagation delay, clock to TTL low  | t <sub>pHL</sub> | 6     | 14   | ns    | $V_{CC} = 5.0V (25^{\circ}C)$                          | 6     |

| Propagation delay, clock to TTL high | t <sub>pLH</sub> | 6     | 14   | ns    | $V_{CC} = 5.0V (25^{\circ}C)$                          | 6     |

| Propagation delay, MS to TTL high    | t <sub>p</sub>   |       | 17   | ns    | $V_{CC} = 5.0V (25^{\circ}C)$                          | 6     |

| Modulus control set-up time          | ts               | 4     |      | ns    | $V_{CC} = 5.0V (25^{\circ}C)$                          | 3, 6  |

| Modulus control release time         | t <sub>r</sub>   | 4     |      | ns    | $V_{CC} = 5.0V (25^{\circ}C)$                          | 4, 6  |

| TTL output rise time (20% - 80%)     | t <sub>TLH</sub> |       | 5    | ns    | $V_{CC} = 5.0V (25^{\circ}C)$                          | 6     |

| TTL output fall time (80% - 20%)     | t <sub>THL</sub> |       | 5    | ns    | $V_{CC} = 5.0V (25^{\circ}C)$                          | 6     |

|                                      | ı                | ı     | 1    | 1     |                                                        | ı     |

#### **NOTES**

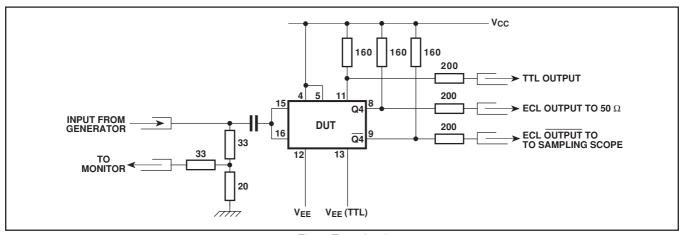

- 1. The temperature coefficients of  $V_{OH} = +1 \cdot 2mV/^{\circ}C$ ,  $V_{OL} = +0 \cdot 24mV/^{\circ}C$  and of  $V_{IN} = +0 \cdot 8mV/^{\circ}C$ . 2. The test configuration for dynamic testing is shown in Fig.6.

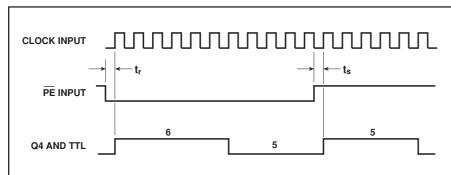

- 3. The set-up time t₅ is defined as the minimum time that can elapse between L→H transition of control input and the next L→H clock pulse transition to ensure that the  $\div 10$  mode is obtained.

- 4. The release time  $t_r$  is defined as the minimum time that can elapse between  $H \rightarrow L$  transition of control input and the next  $L \rightarrow H$  clock pulse transition to ensure that the  $\div 11$  mode is obtained.

- 5. Tested at +25°C and +125°C only.

- 6. Guaranteed but not tested.

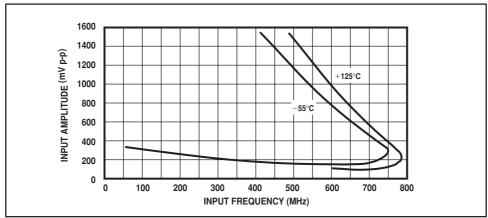

Fig. 3 Typical input sensitivity

| MS | Clock inhibit | <u>PE1</u> | PE2 | Output response      |

|----|---------------|------------|-----|----------------------|

| Н  | Х             | Х          | Х   | All outputs set high |

| L  | Н             | Х          | Х   | Hold                 |

| L  | L             | L          | L   | ÷11                  |

| L  | L             | Н          | L   | ÷10                  |

| L  | L             | L          | Н   | ÷10                  |

| L  | L             | Н          | Н   | ÷10                  |

Fig. 4 Truth table and timing diagram

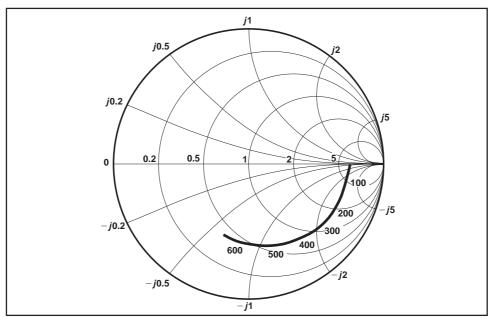

Fig. 5 Typical input impedance. Test conditions: Supply Voltage = 5V, Ambient Temperature =  $25^{\circ}$ C. Frequencies in MHz, impedances normalised to  $50\Omega$ .

Fig. 6 Test circuit

#### **OPERATING NOTES**

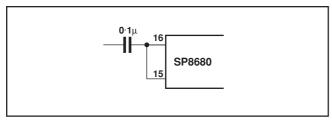

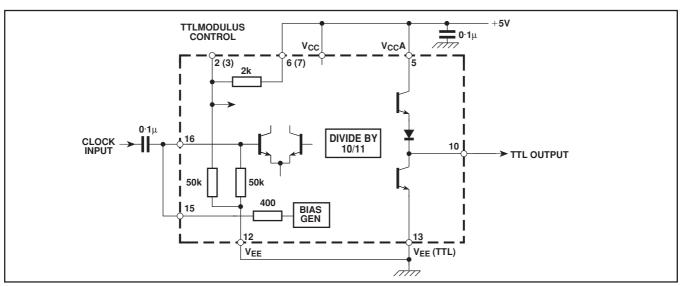

- 1. The clock input, which is ECL10K compatible throughout the temperature range  $-55^{\circ}$ C to  $+125^{\circ}$ C, can also be coupled to TTL as shown in Fig. 9. The clock can also be capacitively coupled to the signal source (see Fig, 7). Connecting the internally-generated bias voltage to the clock input i.e., pin 15 to pin 16, centres the clock input about the switching threshold (see Fig. 8).

- 2. The two complementary outputs are ECL10K compatible but internal pulldown resistors are not included and therefore external pulldown resistors to  $V_{\text{EE}}$  are required.

Fig. 7. AC coupled input

- 3. The TTL totem pole output operates with the same supply and is powered up by connecting  $V_{EE}$  (pin 12) to TTL  $V_{EE}$  (pin 13). If the TTL output is not required then the TTL  $V_{EE}$  pin should be left open circuit, reducing the power consumption by 20mW, typically.

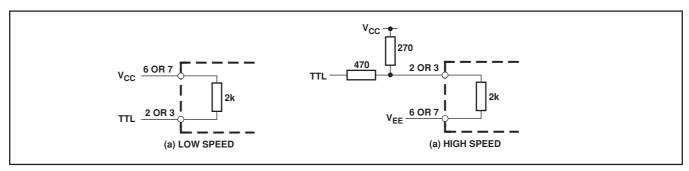

- 4. Both control inputs (<u>PE1</u> and <u>PE2</u>) are ECL10K compatible throughout the temperature range. Each control input is provided with a pullup resistor, the remote ends of which are connected to pins 6 and 7, respectively. This allows the pullup resistors to be unused if so desired or to be used to interface from TTL (see Fig. 9). If interfacing to ECL is required then pins 6 and 7 should be left open circuit; alternatively, they can be connected to  $V_{EE}$  to act as pulldown resistors. When high, the master set input sets the divider to the eleventh state, is asynchronous and overrides the clock input.

- 5. All the inputs have internal  $50k\Omega$  pulldown resistors.

- 6. The circuit will operate down to DC but inputslew rate must be better than  $20V/\mu s$ .

- 7. Input impedance is a function of frequency. See Fig. 5.

Fig. 8 Typical application showing TTL interfacing.

Fig. 9 TTL interface to PE1 and PE2

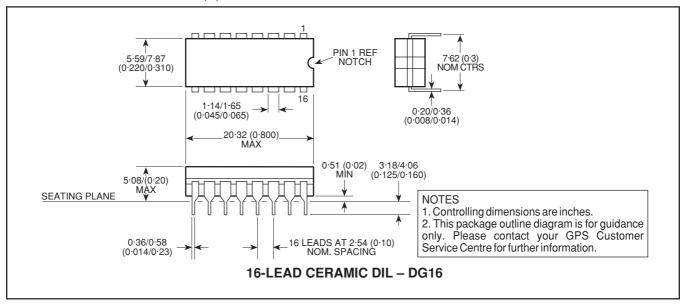

#### **PACKAGE DETAILS**

Dimensions are shown thus: mm (in).

# HEADQUARTERS OPERATIONS GEC PLESSEY SEMICONDUCTORS

Cheney Manor, Swindon, Wiltshire SN2 2QW, United Kingdom. Tel: (0793) 518000

Fax: (0793) 518411

#### **GEC PLESSEY SEMICONDUCTORS**

P.O. Box 660017 1500 Green Hills Road, Scotts Valley, CA95067-0017 United States of America. Tel (408) 438 2900 Fax: (408) 438 5576 CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- **GERMANY** Munich Tel: (089) 3609 06-0 Fax : (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

- JAPAN Tokyo Tel: (3) 5276-5501 Fax: (3) 5276-5510

- NORTH AMERICA Scotts Valley, USA Tel: (408) 438 2900 Fax: (408) 438 7023.

- SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872

- SWEDEN Stockholm Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- UK, EIRE, DENMARK, FINLAND & NORWAY Swindon Tel: (0793) 518510 Fax: (0793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1994 Publication No. DS3644 Issue No. 1.2 March 1994

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee expresso rimplied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior knowledge the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.